High-speed backplane designers face several key challenges such as signal attenuation, inter-symbol interference (ISI), and crosstalk. Products on chip with innovative signal conditioning techniques, such as high-speed backplane interface solutions, can effectively address these system-level challenges, enabling system vendors to provide their customers with high-performance and scalable systems with reduced development time and cost.

High-speed backplanes in modular chassis-based systems such as routers, Ethernet switches, and storage subsystems require high levels of signal integrity and increased system throughput. System vendors for these applications are facing numerous challenges to design these high-speed backplanes in an economical and timely manner. They must also protect their customers’ investments in legacy line cards, chassis, and power supplies, while supporting higher performance and providing newer services.

Today, backplanes in some systems are running on serial link technology at 5Gbps or faster. To design highly reliable systems that can operate at these rates requires chip vendors to provide solutions that ensure error-free transmission in the backplane. This paper will describe high-speed backplanes in modular chassis-based systems and their design challenges, and will discuss silicon solutions that address these challenges.

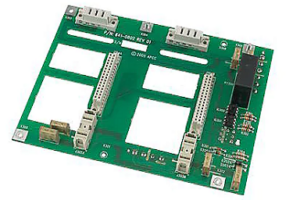

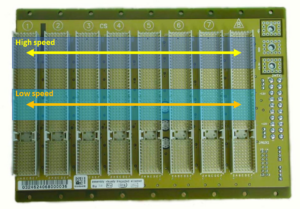

Examples of modular chassis-based systems

Modular chassis systems such as core routers, enterprise switches, and storage subsystems all have high-speed backplanes and multiple line cards. By adding more line cards and increasing the density of line card ports, system performance and capacity can be increased. These systems are modular and can be expanded independently. They are also designed for high availability to ensure continuous operation.

These systems consist of slots with redundant switch cards, line cards, and power modules. They can be equipped with redundant components to increase the reliability and availability of the installation. Backplane interface solutions (also known as high-speed serial connections) provide high-speed, full-duplex communication between backplanes. The speed of the serially connected devices depends on the system throughput requirements. The serial connection transmits data via a high-speed differential signal. This differential signal is then routed through a line card and connector, across the backplane and through another set of high-density connectors. The channel characteristics depend on the backplane material, connector density, alignment width/coupling, etc. In a typical router, the alignment length can range from 1″ to 48″ depending on where the line card is inserted into these alignments.

The backplane interface devices in these modular chassis systems have some key requirements:

1. Increased speed: Interface devices should be able to meet the increasing bandwidth requirements of system designers. Chip vendors are now selling 3.125-5Gbps rates and are offering samples of 6.25Gbps solutions to enable upgrades to existing solutions in backplanes. With a simple switch card upgrade, system vendors can reuse existing chassis and line cards while providing an upgrade path to higher bandwidth line cards to provide more services to customers at a lower cost;

2. Backward compatibility: Backplane interface devices are required to operate at the original line card speed to be compatible with the original line card;

3. High density and low power consumption: To cope with the increasing

3. High density and low power consumption: To cope with increasing network traffic, these systems require smaller footprint and higher performance and density without additional power consumption. So there is always a need for lower power, faster backplane devices.

4. Manufacturability and testability: Backplane interface devices need to integrate features such as JTAG and BIST to enable chip-level and system-level testing during prototyping and manufacturing.

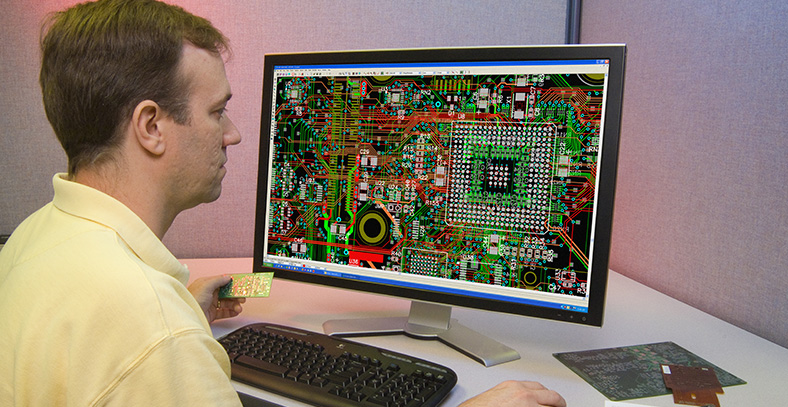

High-speed backplane design considerations

As data rates move beyond the 1Gbps level, designers must address new issues in the design of their backplane systems. The signal integrity of these backplanes is affected by skinning effects, dielectric loss, greater noise due to crosstalk, and inter-symbol interference (ISI).

Skinning effect is a phenomenon where most of the current will be concentrated on the external conductor as the frequency increases. The loss caused by skin effect is proportional to the square root of the frequency, width and height of the alignment.

Dielectric loss is caused by the thermal loss of the plate dielectric and increases linearly with frequency. At higher frequencies, dielectric losses become a more serious problem. These losses not only reduce the amplitude of the signal but also slow down the edge speed of the signal, which in turn causes signal dispersion and poor jitter tolerance.

Because the less attenuated low-frequency components are added to the more attenuated high-frequency components at the receiver, the signal divergence will lead to inter-symbol interference. As a result, its eye diagram opening becomes smaller and therefore more difficult to recover at the receiver, leading to unacceptable BER. This limits the maximum bit rate. Another way to explain this phenomenon is that the signal becomes “dirty” or divergent, resulting in a bit-by-bit drop in energy and thus in BER. At lower rates, the ISI can be corrected because there is enough timing margin. However, at higher rates, ISI is no longer limited to the signal boundaries, but can affect the entire bit width.

The primary source of noise is crosstalk caused by high density connectors and backplane alignments. Crosstalk is a major source of noise caused by high density connectors and backplane layout wiring. There are two types of crosstalk: near-end crosstalk (NEXT) and far-end crosstalk (FEXT). NEXT is caused when a signal from a transmitter close to the victim receiver interferes with the received signal, and FEXT is caused when the received signal is interfered with by a “remote transmitter” connected to the victim receiver. circuits to compensate or eliminate. These circuits compensate for signal loss by attenuating the low-frequency components and amplifying the high-frequency components.

Innovative Signal Conditioning Techniques

The key role of backplane interface devices is to address channel impairment issues such as loss and crosstalk, and thus extend the lifetime of the backplane. The interface transmitter has signal conditioning circuitry such as amplitude control and pre-emphasis.

Similarly, backplane interface receivers use equalization techniques to control loss. In addition, these devices require testable features such as JTAG and BIST to enable system-level testing at the time of manufacture. National Semiconductor’s quad 5Gbps SerDes meets all of these requirements. The signal integrity techniques used in the quad 5Gbps backplane transceiver SCAN50C400 pair and other high-speed backplane interface devices are described in detail below.

Pre-emphasis and de-emphasis: This technique pre-distorts the signal before it is sent to make the signal quality at the receiver as good as the original send. Pre-emphasis raises the high-frequency component and lowers the low-frequency component when the signal is held at the DC level for more than one bit. In designing these methods, the system designer must carefully control the output amplitude to limit the output power.

Receive equalization: Receive equalization compensates for the loss characteristics of the channel by applying relative frequency characteristics to the input data. There are two types of equalization circuits: fixed and adaptive. Fixed equalizers set the compensation characteristics manually, while adaptive equalizers use an adaptive algorithm to set the optimal compensation characteristics, which allows the user to apply one device to a variety of different channels. It can also automatically compensate for manufacturing deviations and changes in channel characteristics brought about by environmental changes.

The receive equalization function can be either integrated into a backplane interface device or executed in a standalone device. The advantage of performing receive equalization in a standalone device is that it provides optimal cabling benefits and design flexibility.

Crosstalk Noise Cancellation: In addition to pre-emphasis and receive equalization techniques, crosstalk cancellation techniques are also used in some systems. These chips use a noise cancellation mechanism that samples noise on neighboring channels and then subtracts it from the signal.