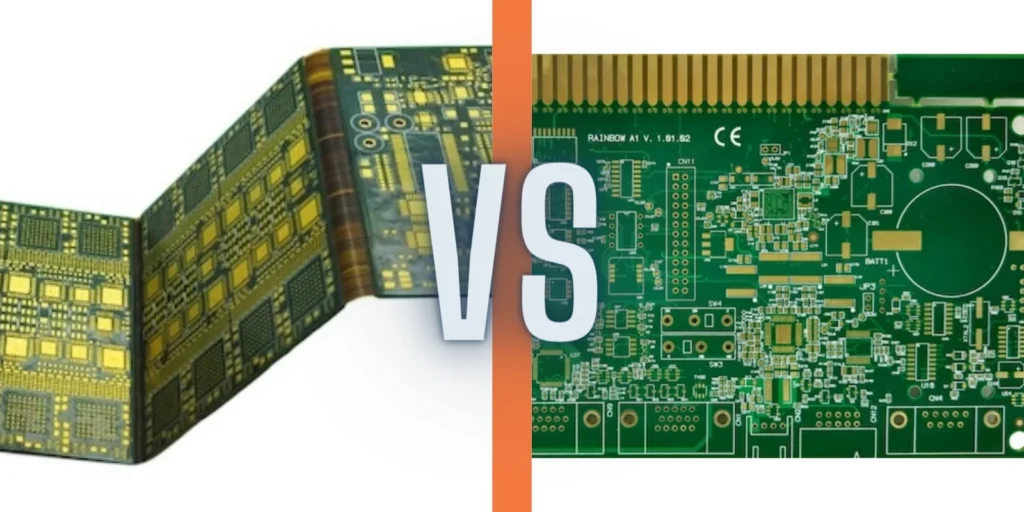

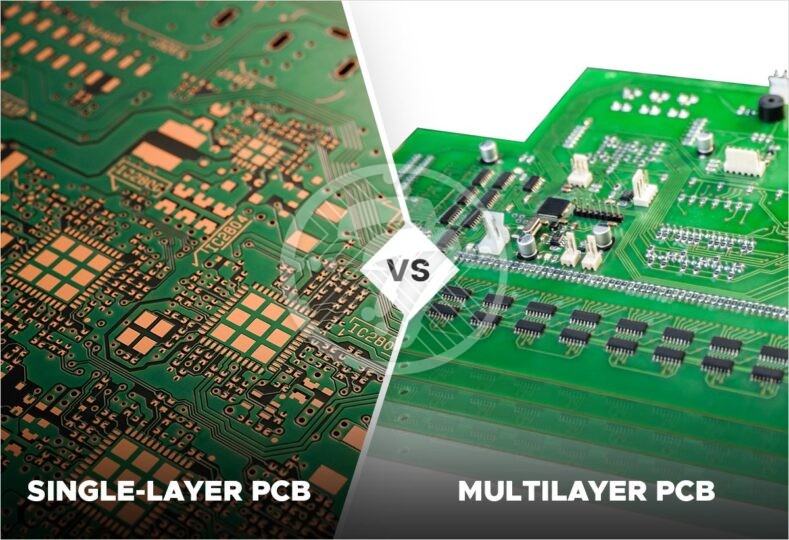

This article lists a variety of different design oversights, explores the causes of circuit failure for each, and gives suggestions on how to avoid these design flaws. This article uses a double layer PCB with FR-4 dielectric, 0.0625in thickness, and a grounded bottom layer of the board as an example. The operating frequency is in various bands between 315MHz and 915MHz, with Tx and Rx power between -120dBm and +13dBm.

Inductive direction

When two inductors (or even two PCB alignments) are in close proximity to each other, there will be mutual inductance. The magnetic field generated by the current in the first circuit will excite the current in the second circuit (Figure 1). This process is similar to the interaction between the primary and secondary coils of a transformer. When two currents interact through a magnetic field, the resulting voltage is determined by the mutual inductance LM:

Equation YB is the error voltage injected into circuit B, and IA is the current acting in circuit A.1 LM is very sensitive to circuit spacing, inductive loop area (i.e., flux), and loop orientation. Therefore, the best balance between a compact circuit layout and reduced coupling is to correctly align the orientation of all inductors.

The magnetic lines in Figure 1 show that the mutual inductance is related to the orientation of the inductor arrangement.

Orient circuit B so that its current loop is parallel to the magnetic lines of circuit A. To achieve this, try to make the inductors perpendicular to each other.

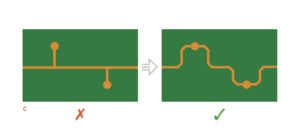

Two different PCB layouts are shown in Figure 2, one of which has components arranged in an illogical orientation (L1 and L3), while the other has a more appropriate orientation.

The following principles should be followed: inductors should be spaced as far apart as possible; inductors should be arranged at right angles to minimize crosstalk between inductors.

Lead coupling

Just as the orientation of the inductor arrangement affects magnetic coupling, so does the coupling if the leads are too close to each other. One of the main concerns of RF circuits is the alignment of sensitive system components, such as the input matching network, the resonant slot path of the receiver, the antenna matching network of the transmitter, etc.

The return current path must be as close as possible to the main current path to minimize the radiated magnetic field. This layout helps to reduce the current loop area. The ideal low resistance path for the return current is usually the grounded area below the leads – effectively limiting the loop area to the dielectric thickness times the lead length. However, if the ground area is split, the loop area increases (Figure 3). For leads that cross the split region, the return current will be forced through the high resistance path, greatly increasing the current loop area. This layout also makes the circuit leads more susceptible to mutual inductance.

Parasitic inductance tends to have a significant impact on the connection of the bypass capacitor. An ideal bypass capacitor provides a high frequency short between the power and ground layers, however, a non-ideal vias can affect the low inductance path between the ground and power layers. A typical PCB vias (d=10 mil, h=62.5 mil) is approximately equivalent to a 1.34nH inductor.

Other problems arise when sensitive circuits share vias, such as two arms of a π-type network. For example, if an ideal cross-hole equivalent to the collector inductor is placed, the equivalent schematic is very different from the original circuit design (Figure 6). As with crosstalk in the shared current path3, this leads to increased mutual inductance and increased crosstalk and feedthrough.

Figure 6 shows an ideal architecture compared to a non-ideal architecture, with potential “signal paths” in the circuit.

Principles to be followed: ensure modeling of vias inductance in sensitive areas; use separate vias for filters or matching networks; thinner PCB copper cladding will reduce the effect of vias parasitic inductance.

Ground and fill

The ground or power layer defines a common reference voltage that powers all components of the system through a low resistance path. Equalizing all electric fields in this manner produces a good shielding mechanism.

DC current always tends to flow along the low-resistance path. Similarly, high-frequency currents preferentially flow through the path of lowest resistance. So, for a standard PCB microstrip line above ground, the return current tries to flow into the ground region directly below the leads. As described in the lead coupling section above, the cut ground region introduces all kinds of noise, which in turn increases crosstalk through magnetic coupling or converging currents (Figure 7).

Filled ground, also known as protective wire, is commonly used in designs where it is difficult to lay a continuous ground area in a circuit or where shielding of sensitive circuits is required (Figure 8). The shielding effect is increased by placing ground vias (i.e., vias arrays) at the ends of the leads, or along the line. Do not mix protective wires with leads designed to provide a return current path; such a layout can introduce crosstalk.

A copper-clad area can limit its effectiveness when it is not grounded (floating) or when it is grounded only at one end. In some cases, it can create parasitic capacitance, altering the impedance of surrounding wiring or creating a “potential” path between circuits, which can have a detrimental effect. In short, if a copper cladding (non-circuit signal alignment) is laid on the board to ensure a consistent plating thickness. Copper clad areas should be avoided as they can affect the circuit design.

Finally, make sure to consider the effects of any grounded areas near the antenna. Any monopole antenna uses grounded areas, alignments, and vias as part of the system equalization, and non-ideally equalized cabling can affect the radiation efficiency and direction of the antenna (radiation template). Therefore, the grounded area should not be placed directly underneath the monopole PCB lead antenna.

The following principles should be followed: try to provide a continuous, low-resistance grounding area; ground both ends of the filler line and try to use an over-hole array; do not float copper-clad wires near RF circuits and do not lay copper skin around RF circuits; if the board includes multiple ground layers, it is best to lay a ground over-hole when the signal line overruns from one side to the other.