The process of PCB design is concerned with the rate at which they access data, the details of this rate relationship, PCB design in order to reduce crosstalk, try to maximize the spacing of signal lines; the following Guangzhou Club Technology PCB design engineers combined with FLASH

The following PCB design engineers from Guangzhou Jujin Technology combine FLASH, SDRAM, DDR to introduce PCB layout and wiring design points.

PCB layout: The data in the memory is used to be read and written by the controller (CPU, such as DSP, MCU, ARM, FPGA, etc.), so it needs to be combined with the PCB veneer size, device density, and alignment density to set aside subsequent equal-length space and choose the right location for placement.

PCB wiring: first of all, the signal lines should be classified, and then divided into groups, after dealing with these two steps, the subsequent fan holes, alignment and winding equal length, etc., the same group according to the unified standard processing on the line. Here the signal lines are divided into three categories: data signals, address signals, control signals. For PCB design engineers, the first step is to develop the ability to identify the type of signal in the schematic diagram, to be able to group the classified signal lines in the PCB wiring. The common grouping method: data group and address group.

FLASH Design

Flash rate is generally low, so the layout and wiring is more relaxed; Flash DQxx is the data signal; Axx is the address signal; Flash layout placement, try to leave enough space for fan holes, fan lines and winding equal length;

There are three things to keep in mind when laying out Flash:

a. Flash signal lines need to control the impedance, which is 50Ω;

b. Signal line spacing of 3W if space allows;

c. Equal length control range: within 10 mil;

Two signals to note are DQML and DQMH , which are mask signals for data signals and belong to the low 8 bits and high 8 bits, respectively. So when grouping, add them to the low 8-bit group and the high 8-bit group, respectively. This way each data group will have 9 signal lines.

SDRAM layout: try to keep the signal lines not too long and placed close to the controller;

For a 1-chip SDRAM, use a “point-to-point” topology.

As for the topology of the two slices, see the layout of the DDR2 design below. The layout should be flexible, and it’s best to be able to cite one or the other.

SDRAM cabling:

a. Grouping: Based on the data classification described earlier, data groups can be divided into two groups of low 8 bits and high 8 bits:

Low 8 bits: (BUS name can be customized with a meaningful name): D0~D7, DQML, 9 signal lines in total;

High 8 bits: D8~D15, DQMH, 9 signal lines in total;

Note: Sometimes the network names may not be named this way and should be able to be recognized as such;

Address and control signals are grouped together;

b. The signal line control impedance is 50Ω, maintaining a full reference plane;

c. Widen the signal line spacing to maintain 3W spacing;

d.Equal length control: equal length with reference to clock;

e.Equal-length error control range: data group: 10 mil; address group: 10 mil;

f. Add some reflow ground vias near the signal layer change;

DDR design

DDR can be seen as an upgrade from SDRAM, in comparison, the data line grouping appears as low 8-bit latch signal (LDQS) and high 8-bit latch signal (UDQS) respectively, at this point each group has 10 signal lines now; while address, control, and clock are still in one group.

And DDR2 is an upgrade from DDR with a higher data exchange rate; there are also some changes in the pinout: the single-ended signal latch signal of DDR becomes a pair of differential signals, so that the data team has 11 signal lines per group.

Another change is the change in operating voltage, typically 3.3V for FLASH, 2.5V for SDRAM/DDR, 1.8V for DDR2, to 1.5V for DDR3 later on, as the lower voltage allows for faster level flipping.

DDR2 wiring

Similar requirements to SDRAM; with a few variations:

a. Differential signal impedance control of 100Ω due to the availability of differential signal lines;

b. The differential needs to be made equal in pairs, with the error controlled to 5 mil;

c. Equal-length error control range required is higher: data line:10mil; address:10mil;

d. Please note the VREF power supply, this alignment requires a thicker 15~30mil; filter capacitors are placed close to the DDR pins;

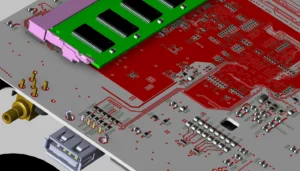

DDR2 layout

The layouts of FLASH and SDRAM were described separately earlier, with a point-to-point layout for only 1. The layout is also more fixed in the presence of multiple devices. (The device spacing is controlled by the layout operator.) With 2 memory particles, there are two ways: symmetrical placement about the controller and top-bottom pair-paste placement.

The topology of the address signal, which we usually call the far branch, is also called the “T” topology, where the address signal is first received in the middle and then split to the DDR on both sides, with the VIA in the middle called the T point;

When space is limited, with a top-bottom pair layout, the address part can still use the “T” topology sector hole above, while the data part sector hole is more problematic and needs to be adjusted manually.

When there are four DDRs, the layout idea is similar to two: enough space, put them on the same side, at this point pay attention to the location of the T-point; when space is more limited, first two-by-two paste, and then use the T-topology;

There is another form of topology: daisy-chaining, which is usually used more often in DDR3 layouts; there is also a form of daisy-chaining: the controller drives multiple loads, such as a CPU with SDRAM behind it, and nightly FLASH, which uses a daisy-chain topology: CPU–SDRAM—FLASH, prioritizing the signal topology that guarantees a high rate.

As for DDR layout, there are many more derived layouts, such as 5 DDR2s, one of which is for error correction and is usually placed in the middle, its address line is no longer placed with the other 4 when doing equal length, and the other 4 memories can form a more perfect T-shaped topology.

The above information is summarized by Guangzhou Jujin Technology Co., Ltd. PCB design engineers for your PCB memory module design, hope that all help you.